最近很多人都在聊半導體市場又成長了多少、市值衝到幾千億美金什麼的... 說真的,我自己是覺得,那些數字根本不是重點。

真正的故事,其實跟生存有關。

因為未來十年,能活下來而且稱霸的,不會是那些只會出貨更多晶片的公司。而是那些... 嗯,徹底重新設計「晶片是怎麼被製造出來」的公司。而這場革命的核心,沒別的,就是 AI。

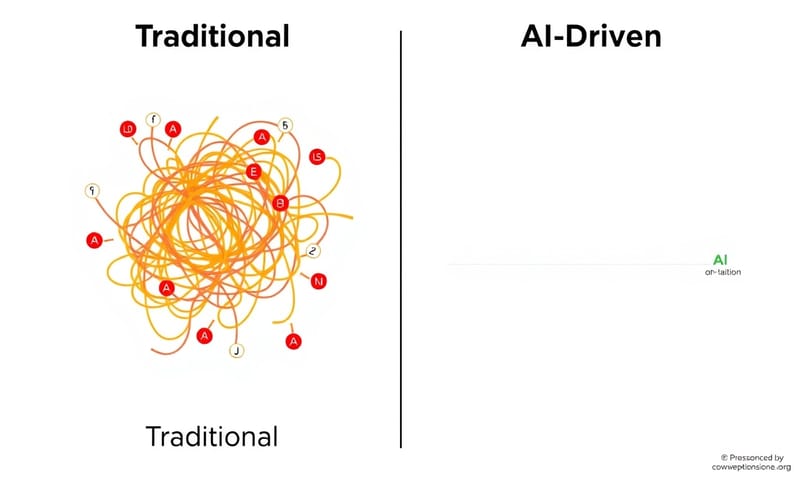

說真的,傳統方法已經撞牆了

以前大家講摩爾定律,好像很神,每隔一段時間晶片就能塞進兩倍的電晶體。這幾十年來,靠著 EDA (電子設計自動化) 工具,工程師們也確實一路從 10 奈米、7 奈米推進到 5 奈米。但... 現在不一樣了。

當我們談到 3 奈米甚至更小的製程時,你會發現,老方法真的不行了,整個設計流程就像卡住了一樣。這不是誇張,你想想看:

- 晶片的複雜度,從以前大概幾百億個電晶體,現在... 嘖,動不動就破兩三千億個。那個量級完全不同。

- 一個設計的驗證週期,以前可能幾個禮拜,現在拖到幾個月是家常便飯。

- 然後最讓人頭痛的 design closure,就是那個要把所有設計收斂到符合標準的階段,感覺不管怎麼加班都搞不定,永遠有新的問題冒出來。

但市場根本不等人。那些做 AI 伺服器、雲端服務的大廠,他們不可能等個兩三年才拿到下一代晶片。他們要的是幾個月內就看到東西。這種「複雜度爆炸」跟「上市時間壓縮」的雙重壓力,真的讓傳統的 EDA 流程快要崩潰了。

你看,已經有人在超車了

這不是未來式,是現在進行式。有些公司不只是在適應,他們根本是靠著 AI 開始甩開對手了。

比方說,三星(Samsung),我看到資料說他們導入 AI 工具後,晶片最重要的 PPA 指標(功耗、效能、面積)直接拉高了大概 8% 到 11%。你知道嗎,在晶片設計的世界裡,這幾個百分點簡直跟黃金一樣珍貴。

還有微軟(Microsoft),他們用了 Synopsys 的 AI Copilot,把驗證工作的速度提升了 10 倍。對,你沒看錯,10 倍。以前要搞好幾個月的事情,現在可能幾個禮拜就搞定了。

然後是 Intel,他們也透過 AI 把設計迭代的週期從「月」縮短到「週」。在這種分秒必爭的競賽裡,省下幾個禮拜的時間,那個優勢就很可怕了。

這些都不是小小的勝利,這是一種根本上的轉變。而且這種優勢會像滾雪球一樣。一旦你的開發週期縮短,你的下一代產品就能更快問世。一旦 AI 幫你優化了設計,你的團隊就有餘力去處理更多專案。時間一長,領先者跟落後者的差距只會越來越大。

所以,這些 AI 到底是什麼狠角色?

OK,所以這些聽起來很神的 AI 工具,到底是什麼東西?目前市場上主要有幾個玩家,他們的思路其實不太一樣。我把它們整理一下,這樣比較好懂。

| AI 工具 | 它主要是幹嘛的? | 用白話文講就是... | |

|---|---|---|---|

| Synopsys DSO.ai | 用「強化式學習」來探索數萬億種設計參數組合,自動優化晶片的 PPA。 | 與其讓工程師一個個參數慢慢猜、慢慢試,DSO.ai 就像一個超會下圍棋的 AlphaGo,只是棋盤換成了晶片佈局。它自己會去試錯,然後找出人類很難想到的最佳解。 | |

| Cadence Cerebrus AI Studio | 提供一個「代理人 AI 平台」,讓 AI 們可以自主處理整個 SoC 的實現流程。 | 這個更猛。它不只是一個工具,比較像是一個「AI 團隊」。一個人類工程師可以當工頭,監督好幾個 AI 小弟,同時去搞定晶片的不同區塊。人力直接被解放了。 | |

| Synopsys.ai Copilot | 用大型語言模型(LLM)當作工程師的智慧助理,幫忙寫程式碼、查規格、回答問題。 | 這個主要是幫「人」的。就像有個超資深的學長坐在你旁邊,你卡關的時候可以隨時問他。菜鳥工程師可以更快上手,資深工程師也不用再浪費時間做一堆雜事。 |

你看,這三者的切入點完全不同。一個是專攻「最佳化」,一個是改變「工作流程」,另一個是提升「人的效率」。但合在一起,就變成一股很可怕的力量。

那台灣呢?我們的位置在哪?

說到這個,我就會想到台灣的狀況。你知道的,台灣在半導體超強,尤其在「製造」這塊,有台積電這個護國神山,沒人敢嘴。

不過呢,這波 AI 革命的浪潮,核心是發生在更前端的「設計」領域。你看,主導這些 AI 工具的,像是 Synopsys、Cadence,都是美國的 EDA 大廠。像 IEEE Spectrum 這種國際期刊也一直在提,未來的競爭力會越來越倚重軟體和演算法。這跟台灣過去靠著精良製程、強大產能和管理效率領先的模式,嗯,老實說有點不一樣。

這不是說製造不重要了,完全不是。而是戰場被擴大了。當晶片設計本身可以用 AI 加速、優化到極致時,設計端的創新速度,會變得跟製造端的良率一樣關鍵。對台灣的 IC 設計公司來說,這既是挑戰,也是個不得不跟上的機會吧。怎麼把這些超強的 AI 工具用得比別人好,可能會是接下來幾年很重要的一件事。

從「AI 輔助」到「AI 自主」

好,拉回來。那接下來會怎麼走?

現在我們大部分看到的,都還在「AI 輔助」的階段。就是說,主要還是人在開車,AI 只是提供導航、幫忙踩油門。但下一步,很明顯就是朝「AI 自主」前進了。

可以想像兩個蠻酷的場景:

- 多個 AI 互相合作:想像一下,一個 AI 專門負責省電,另一個 AI 專門衝效能,還有一個 AI 專門顧良率。它們會像一個真正的人類團隊一樣,互相溝通、吵架、妥協,最後找出一個對整個晶片來說最好的全域最優解。

- 跨領域的整合優化:現在的晶片設計,類比、數位、系統層級,常常還是分開來搞。未來 AI 有可能跨越這些界線,從一開始就把所有東西整合在一起思考,提早發現不同領域之間的衝突,做出更聰明的取捨。

這聽起來好像很科幻,但其實... 看看那些用強化式學習的工具已經能搞定整個流程,就知道這一天可能比我們想的還快到來。

這不只是工程師的事

所以,聊了這麼多,我自己是覺得,這整件事不只是工程師換個工具那麼簡單。它比較像是一場生存遊戲。

晶片是所有現代科技的基石,手機、汽車、雲端伺服器、醫療設備... 還有我們現在天天在玩的那些大型 AI 模型,底下全都是靠晶片在跑。如果晶片設計的速度慢下來,那所有產業的創新都會跟著慢下來。

反過來說,如果晶片設計能用 AI 加速,那就等於是幫整個科技世界裝上了渦輪引擎。

這就是為什麼領導者要煩惱。問題已經不是「我們該不該用 AI?」,而是「我們到底要多快才能把整個團隊和工作流程都翻新?不然對手就要超車到看不見了」。

這場革命已經開始了,真的沒在等人的。

最後想問問大家,如果你是第一線的設計工程師,上面提到的三種 AI 工具(DSO.ai 的自動優化、Cerebrus 的 AI 團隊、Copilot 的個人助理),你覺得哪一個對你的工作衝擊最大?或是你覺得哪個最讓你感到興奮(或焦慮)?在下面留言分享你的想法吧!🤔